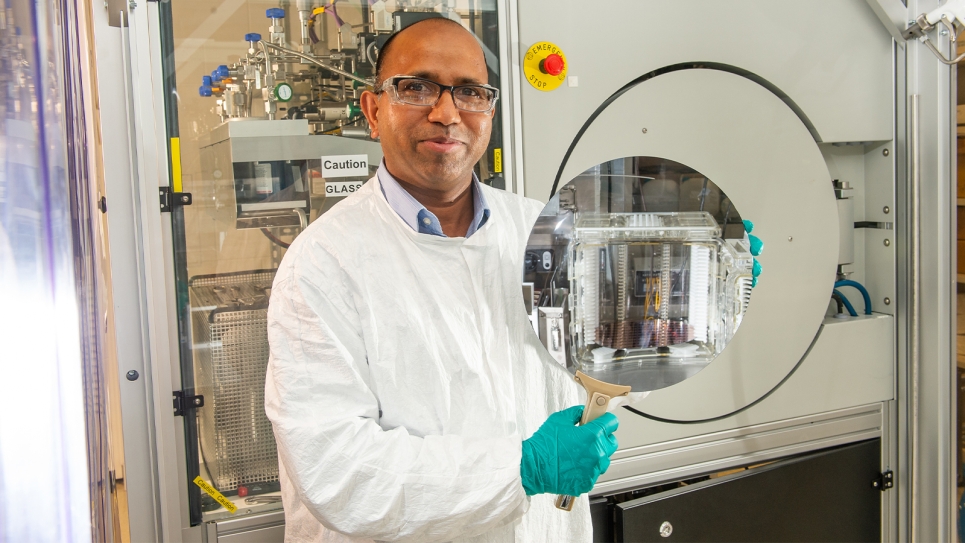

Argonne Senior Scientist Anil Mane holds a 300 mm silicon wafer coated by atomic layer deposition using the instrument in the background. (Image by Argonne National Laboratory.)

As part of the effort, researchers will carry out simulations on ALCF supercomputers to assess the energy savings and performance of new materials and devices for next-generation microchips.

While the microchips inside electronic devices like cell phones and computers are incredibly small, transistors — the tiny electrical switches inside of microchips — are approaching the atomic level. Today’s microchips pack over 100 million transistors in an area the size of a pin head.

Despite their almost unimaginable size, the total number of such microelectronic devices consume an enormous amount of energy, which is growing exponentially. Predictions indicate that 20% of the world’s energy could be consumed by microelectronics by 2030.

Averting this crisis hinges on developing new transistors, materials and manufacturing processes to create ultra-low-energy microchips. Recently, the U.S. Department of Energy (DOE) awarded DOE’s Argonne National Laboratory $4 million to fund research that will use atomic layer deposition (ALD) to advance new materials and devices for creating microchips that use up to 50 times less energy than current chips.

Set to launch in early 2024, the project — which will last two and a half years — is funded by the Energy Efficient Scaling for Two Decades (EES2) program of the DOE’s Advanced Materials and Manufacturing Technologies Office. Argonne will partner with Stanford University, Northwestern University and Boise State University on the project. Argonne Distinguished Fellow Jeffrey Elam, who founded and directs Argonne’s groundbreaking ALD research program, will lead the research team.

“It is only recently that microelectronics started using a large fraction of the Earth’s electricity,” said Elam. “This is an urgent problem. DOE is committed to finding energy-efficient solutions that will flatten the demand curve for electricity use by microelectronics.”

Advanced technology, including the artificial intelligence (AI) explosion, is speeding up the pace at which energy is used in computing. AI applications analyze massive amounts of data and consume large amounts of electricity. As AI becomes widespread, enormous data centers that power those applications will face significant energy increases. The proliferation of “smart” devices and their data requirements also increase electricity use.

“Computers today spend over 90% of their energy shuttling data back-and-forth between the memory and logic functions, which exist on separate chips,” Elam said. “This limitation is known as the ‘von Neumann bottleneck.’ Energy used to move the data is wasted as heat. As computing demand grows, we must develop low-power transistors and microchips to overcome this bottleneck and prevent an energy crisis.”

The project grew from Argonne’s Laboratory Directed Research and Development Program activities and a project funded by the DOE’s Office of Science. Threadwork is a research program that applies co-design to develop neuromorphic devices and terahertz interconnects that will enable high-performance detectors for high energy physics and nuclear physics.

Argonne is a pioneer in ALD, a thin-film deposition technique used extensively in microelectronics manufacturing. ALD produces extremely thin layers — only one-atom thick — to make microelectronics with great precision. These films are considered 2D since they have length and width, but essentially no thickness. A wide variety of thin films can be prepared by ALD on complex, 3D substrates.

“Atomic layer deposition is an ideal technology for fabricating ultra-low power electronics,” said Elam, an ALD researcher for more than 20 years. This makes ALD attractive for uses including lithium-ion batteries, solar cells, catalysts and detectors.

In this project, Argonne scientists will use ALD to redesign the microchip and eliminate the back-and-forth shuffling of data. Scientists want to close the gap between the microprocessor, or “brain,” and the memory chips. 3D integrated circuits can stack the memory and logic layers on top of each other, pancake-style. This could potentially reduce energy usage by 90%.

Currently, silicon is the semiconducting material used to make memory chips and microprocessors, but the 3D integration necessary to stack the layers is extremely difficult to achieve with silicon. Semiconductors control electric currents.

To overcome this limitation, researchers are developing an alternative, 2D semiconducting material, molybdenum disulfide (MoS2), to replace silicon. Building on previous research, Argonne scientists are using ALD to create atomically precise MoS2 films. “We can create extremely thin, 2D MoS2 sheets. These sheets will replace the bulky, 3D silicon thin films used in today’s transistors. This leaves more room on the microchip to effectively stack the memory and logic together, dramatically reducing energy,” Elam said.

Argonne, in collaboration with Boise State University, developed ALD methods for creating 2D MoS2 films. The team will demonstrate the use of MoS2 to create 2D semiconductor field effect transistors (2D-FETs) that can be stacked in 3D. FETs are conventional transistors but are based on 2D rather than 3D materials. This method allows the integration of memory and logic functions not possible with silicon.

Simultaneously, Argonne scientists are demonstrating the use of ALD MoS2 in memtransistors, electronic components used to build neuromorphic circuits. Neuromorphic circuits mimic connections between neurons in the brain to create microchips that use significantly less energy. This technology is relatively new. But neuromorphic circuits have the potential to use one million times less energy compared to conventional silicon devices.

Both 2D-FETs and memtransitors have been successfully demonstrated at the lab scale by growing MoS2 at high temperatures. Argonne scientists want to take the technology to the next level. Commercial manufacturing will require MoS2 to be deposited on large, pizza-sized wafers at low temperatures. In this DOE project, the research team will develop these capabilities to ensure that the MoS2 ALD is compatible with current semiconductor manufacturing processes. This is crucial to accelerating the integration of this technology into future semiconductors.

Scientists at the partner institutions will use their unique expertise to advance specific areas of the project. Professor Eric Pop at Stanford University will develop 2D-FET devices, Professor Mark Hersam at Northwestern University will develop memtransistors that utilize the ALD MoS2, and Professor Elton Graugnard at Boise State University will perform advanced characterization of the ALD MoS2 coatings to evaluate the quality of materials.

In parallel with the experimental work, Argonne is using modeling and simulation to design energy-efficient devices that incorporate ALD MoS2. This work will leverage high performance computers at the Argonne Leadership Computing Facility, a DOE Office of Science user facility at Argonne, to model and simulate circuits integrating 2D materials. The computers will measure energy savings and benchmark their performance against current silicon technologies. Researchers seek to advance the stacked devices toward a pilot-scale demonstration, with the goal of marketing them for commercial use by the microelectronics industry. The project is a new facet of Argonne’s growing portfolio of research and development using ALD technology to address a wide variety of energy challenges.

The Argonne team also includes Physicist Moinuddin Ahmed, Principal Materials Scientist Angel Yanguas-Gil, Computer Scientist Xingfu Wu, Assistant Computer Scientist Sandeep Madireddy and Senior Materials scientist Anil Mane. The project builds on Argonne’s extensive work advancing the science and technology to create the next generation of microelectronics. Along with innovations in energy-efficient microelectronics and architectures, scientists are developing new approaches to energy-efficient and environment-friendly manufacturing for microelectronics.